2023年10月17日,美国商务部产业安全局(“BIS”)就先进计算芯片、超级计算机和半导体制造设备的相关出口管制发布了两个新的临时最终规则(Interim Final Rule,“IFR”)。

即:先进计算物项和超级计算机临时最终规则(“AC/S IFR”)和半导体生产物项临时最终规则(“SME IFR”),以对2022年10月7日所发布的针对中国的半导体出口管制临时最终规则(“10.07 IFR”)进行全面修订。

在10.07 IFR发布时隔一年之后,BIS结合了半导体业界对于10.07 IFR的反馈以及10.07 IFR在实际执行中其所发现的一些具体问题发布这两个新一轮IFR。

在此,我们结合我们在出口管制和半导体领域多年的经验和思考,对本次法规更新中中国公司较为关心的问题进行说明,希望中国企业能对此有清晰的理解,并对企业发展做出正确的判断。

问题一:

本次出口管制新规修订的主要内容是什么?

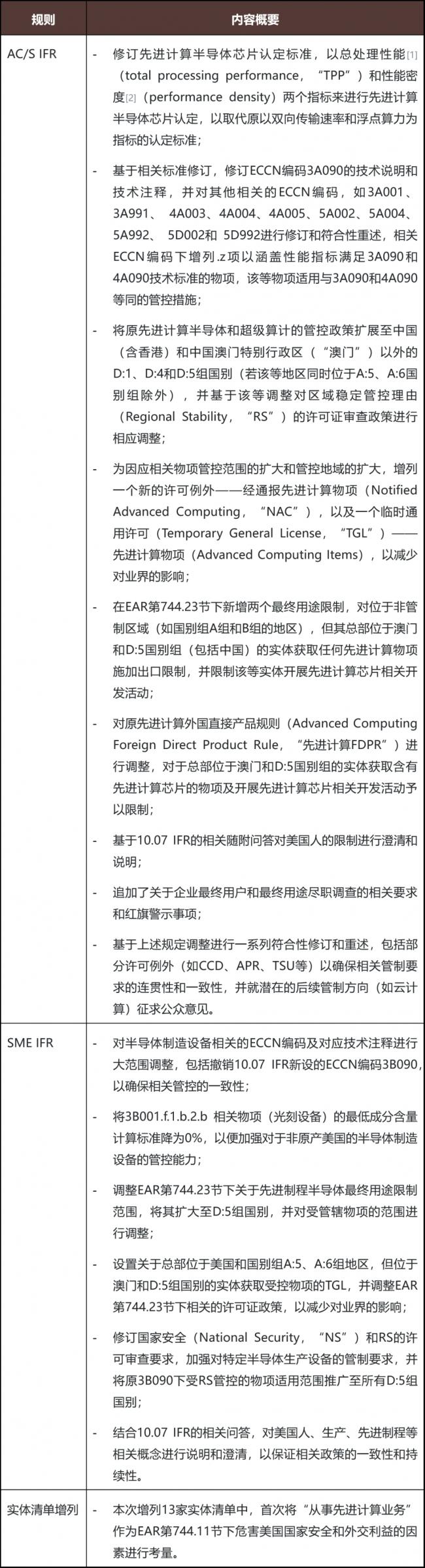

概而言之,本次出口管制规则调整除了包括AC/S IFR和SME IFR外,还包括一个涉及13家中国企业的实体清单规则更新。其具体内容大致如下:

就相关IFR中的具体问题,我们会在下文进行详述。

问题二:

在AC/S IFR下,主要受到影响的芯片类型有哪些?

如前所提示的,由于根据AC/S IFR,BIS本次将采用TPP和性能密度的新指标来进行先进计算半导体芯片的认定,相比于原来单纯以双向传输速率和浮点算力为指标的认定标准,BIS认为现有认定标准更为综合全面,能够有效防范潜在的规避行为。同时,本次BIS在对先进计算芯片进行管控时,采取分类管控的逻辑:首先,对于功能最强大的数据中心集成电路(如3A090.a项下的芯片),BIS 将对位于国别组D:1、D:4或D:5(如该等地区被列入A:5或A:6国别组则除外)下的任何目的地实施出口管制措施,且严格限制其用于数据中心之目的;其次,对于功能较弱但可被资源充足者用于训练大规模人工智能系统的先进集成电路芯片(如 3A090.b下物项 ,以及某些 3A090.a 下物项),BIS将为国别组D:1、D:4或D:5中的目的地提供许可证例外NAC,但使用此类许可证例外将要求出口或再出口至澳门或国家组D:5中指定的目的地时,需履行通报程序,以供BIS进行审查。以3A090下物项为例,相关芯片参数和管控要求的对应关系如下:

需要注意的是,由于先进计算FDPR的限制,根据BIS在诸多场合的表态,在BIS的认知上,由于全球半导体供应链中受EAR管辖的技术和软件发挥着基础性作用,因此,不仅包含原产于美国的芯片,理论上目前市场上所有的先进计算芯片只要满足该等性能指标,即使相关芯片并非在美国境内设计和生产,也将会受本次新规的规制。同时,需要提醒的是,由于本次AC/S IFR在性质上仍属于临时最终规则,BIS在后续仍保留了对相关技术参数进行进一步调整的空间。例如,在本次新规修订过程中,BIS技术咨询委员会(Technical Advisory Committee,“TAC”)曾考虑过以芯片单位面积上的晶体管密度作为先进计算芯片的管控指标,该方案虽然最后并没有在新规中采纳,但在本次AC/S IFR所增列的红旗警示事项中,仍将晶体管密度作为一个重要标准进行提示[3],因此不排除BIS在后续进一步规则修订中,会基于对出口管制措施的实施效果的评估,重新将其作为先进计算芯片的衡量指标。

问题三:

在AC/S IFR下,哪些主体会受到相关出口管制限制措施的影响?

根据本次AC/S IFR的相关调整,基于新的目的地限制和最终用户和最终用途限制,总体上而言,相关出口管制措施针对特定主体的影响如下:

上述相关修订也是本次AC/S IFR最为重要的修订之一。根据BIS的说明,通过将原针对中国的先进计算半导体出口管制限制扩展至D:1、D:4和D:5组国别,能够有效防止通过第三国(诸如阿联酋和沙特等国)向中国违规转运受管制芯片;同时,对总部位于澳门和D:5组国别的实体施加特别的最终用户和最终用途限制,同样能够防止相关实体利用其境外子公司规避美国出口管制限制,继续从事AI开发活动(例如总部位于中国的云服务商和数据服务商在境外的子公司将受到本次新规的限制)。另外,新规中对于3E001技术传输的相关管制要求,同样也会对中国FABLESS厂商的境外研发活动(包括流片),产生严重影响。

需要特别注意的是,本次新规关于这一部分有两个十分关键的立法值得后续关注。首先是关于总部(headquarter)概念的进一步澄清。本次在新规中,将总部作为一个重要的最终用户和最终用途管控标准,但现有EAR中并没有总部的定义。不过,显而易见,BIS在后续总部概念的澄清中不会简单以股权关系来判断相关公司的总部位置,而是将更注重实质的考察。之前美国财政部在对外投资审查中对于受管制外国实体(Foreign Entity of Concern,“FEOC”)的拟议标准可能可以作为总部认定的较好参照,即:如相关公司的综合收入、净收入、资本支出或营业费用支出主要位于中国或其他D:5组地区,那么BIS很可能将认定该公司的总部位于D:5组地区。其次是关于云服务出口管制可能的进一步收紧。虽然在本次新规发布之前,业内曾预计BIS会在新规中同样加入关于云服务出口管制的相关内容,但最终在AC/S IFR中,BIS仅仅限制了部分总部位于D:5组国别的实体进一步获取相关先进计算物项,但是对于基于IaaS的云计算服务(如中国公司租用第三国实体的云计算算力)并没有施加进一步限制,而是作为一个遗留事项交由公众评议。预计BIS很可能后续会就云计算的最终用户和最终用途限制出具单独的限制规定,以进一步填补相关漏洞。

问题四:

相关企业在AC/S IFR下是否还有空间能够减少对自身业务的影响?

BIS本次在公告中说明,为了尽可能减少对业界的影响,在AC/S IFR中设立了新的许可例外NAC和一个新的TGL。企业可以结合自身业务情况来判断NAC和TGL的适用情况。

NAC适用于满足3A090相关参数指标的部分集成电路以及相关软件和技术向D:1、D:4和D:5组国别区域以及总部位于澳门和D:5组国家,但位于其他区域的实体出口、再出口及境内转移。具体而言,其适用要求如下:

根据EAR第740.8(c)节的相关规定程序,向澳门和D:5组地区及相关主体出口可适用NAC许可例外物项时,申请人应至少提前25个日历日在SNAP-R系统填报NAC适用申请,BIS将基于相关申请组织相关部门进行审查,申请人可以在BIS出口许可证申请跟踪系统(https://snapr.bis.doc.gov/stela,“STELA”)中获取待处理的BIS通知审查状态或在SNAP-R系统中核实状态过程。25个日历日内,STELA系统将通知申请人是否适用NAC。

如前所说明的,NAC许可例外不能用于符合3A090.a参数指标的集成电路用于数据中心相关用途。此外,根据EAR第740.8(b)节的规定,该许可例外也不能替代其他许可证要求向根据EAR第744节受限的相关主体(如列入实体清单的实体)提供受控物项,也不能违反EAR第744.21节的相关规定,将相关物项用于支持中国、俄罗斯、委内瑞拉、缅甸、柬埔寨等国的军事最终用户和军事最终用途。

从NAC适用的整个程序来看,与一般许可例外不同,在针对澳门和D:5组国内别及相关实体适用过程中,其实质是一个简易的许可证申请流程,甚至可能会基于审查结果,成为一个许可证审查前置程序。BIS可以继续相关填报信息,持续监控相关地区及相关实体境内先进计算集成电路的应用情况,包括次性能的算力芯片在数据中心中的应用情况,以便于BIS进行相关信息搜集和分析,进而决定下一步的管制措施。而对于相关企业而言,NAC的存在至少为境内外数据中心持续经营保留了可行性,相关企业需要评估次性能算力芯片是否可以满足现有数据中心的运营和发展要求。此外,需要提示的是,NAC不适用于AC/S IFR中对于半导体相关技术在先进计算FDPR下的相关限制,因此NAC并不能解决相关FABLESS企业进行芯片设计研发和流片的问题。

而本次发布的TGL,其主要适用对象为总部未位于澳门和D:5组国别区域的实体在D:1、D:4和D:5组国别区域(不包括国别组A:5和A:6列明区域)内为相关区域外(不含未位于相关区域,但总部位于澳门和D:5组国别区域的实体)提供与以下ECCN编码相关的集成、装配、检测、测试、质保和分销活动:3A001.z;3A090;3D001;3E001;4A003.z;4A004.z;4A005.z;4A090;4D001;4D090;4E001;5A002.z;5A004.z;5A992.z;5D002.z;5D992.z;5E002;5E992。相关TGL的有效期至2025年12月31日。

另外,由于本次AC/S IFR的生效日期为美国东部时间2023年11月17日,而AC/S IFR中并无保留条款(Savings clause), 企业需要注意,如在新规生效之前已订购的相关物项未在新规生效前完成发货,其后的发货(包括装运、转运或国内转让等方式实际交付物品以及授权交付的行为)将会受到新规限制。

问题五:

SME IFR下对于半导体制造设备的管制范围有哪些变化?

相比于AC/S IFR,SME IFR的相关调整内容对半导体制造行业的影响整体仍处于预期范围内。其中主要的调整还是在受管制半导体制造设备的技术参数和指标。本次BIS删除了ECCN 3B090,并在ECCN 3B001和 3B002中替换和扩展了相应规定,以囊括原有3B090下管控设备信息,并在3B001中增加了用于制造半导体制造设备的设备,这反映出BIS对于半导体制造设备的管制并不局限于设备本身,相关受限国家和地区(即澳门和包括中国在内的D:5组国别区域)自身半导体设备研发制造能力也将成为管制重点。与此同时,BIS在本次ECCN编码技术注释的调整中也反映了去年以来与日本、荷兰两国就半导体制造设备管控联动方面的成果。如此次BIS调整后的3B001.f.1.b的DUV性能指标与荷兰半导体出口管制新规中的3B001.f.4物项性能指标一致,3B001.k~p的相关设备管控指标则基本与日本半导体出口管制新规中的相关设备性能一致。同时,为了进一步确保对于半导体设备相关出口管制的范围涵盖最大化,并敦促相关盟友在半导体领域的出口管制措施与美国保持一致,美国此次在SME IFR中最重要的实质性修改之一是调整了ECCN编码3B001.f.1.b.2.b下物项的最低成分含量标准(de minimis rule),将其由25%降至0%。这也意味着在美国境外制造的用于开发或生产先进制程集成电路的光刻设备只要含有美国原产零部件,即将被视为受EAR管辖的物项。不过就这条管控要求,BIS表示可以适用相应例外,即:如果另一个国家对符合3B001.f.1.b.2.b参数的设备保持与美国同等的出口管制政策,则BIS将不再对这些物项施加额外管制。同时,BIS正在计划增加相应注释,发布其认可的维持与美国同等出口管制政策的国家的信息。这一相关例外非常类似EAR中原有的“额外许可再出口”(Additional Permissive Reexports,“APR”),但相比于可以适用于全部A:1国别组(即瓦森纳安排成员国)的APR许可例外,对于光刻设备的许可例外适用范围明显更小,也充分体现了目前美国在出口管制领域“小院高墙”的整体策略。

问题六:

SME IFR下对于企业获取相关半导体制造设备是否有新的限制?

本次SME IFR中对于相关半导体设备分别设置了NS和RS的管控理由,根据EAR第742.4(a)(4)节的相关规定,在NS管控理由下,向澳门或D:5国别组区域出口或再出口ECCN 3B001.a.4,c,d,f.1.b,k至p所列商品及其相关的软件和技术,均须申领许可证。相关要求在EAR第742.6(a)(6)(i)节关于RS的管控理由中同样保持一致。相关许可证政策均参考EAR 第744.23(d)节下的相关要求。根据BIS本次对EAR第744.23(d)节的修订,原则上相关出口许可申请仍将适用推定拒绝的许可证政策。但是如存在不受EAR管辖的外国产半导体制造设备的性能与受EAR管辖的半导体制造设备相当的情形,且最终用户为总部位于美国或A:5、A:6国别组区域的实体(该等实体的主要权益不能为总部位于澳门或D:5国别组区域实体拥有)时,则许可证政策将调整为推定批准。除上述两种情形以外,BIS将采取逐案审批的许可证政策。与10.07 IFR一样,在进行许可证审批时,BIS会考虑技术发展水平、客户情况、合规体系等因素来决定许可证批准与否。另外,与AC/S IFR类似,SME IFR下同样设置了TGL,适用于总部位于美国或A:5和A:6国别组区域内的实体将商业管控目录(Commercial Control List,“CCL”)内的受控物项出口至其位于澳门或D:5国别组区域内的制造工厂,以进行ECCN编码为3B(即半导体制造设备)相关物项的零件、组件或设备的开发和生产活动。该TGL的适用前提包括:

适用TGL的实体其向受限目的地出口的物项仅受反恐(“AT”)原因管控;且

适用TGL的实体的主要权益不能为总部位于澳门或D:5国别组区域实体拥有。

从新的调整来看,对于半导体设备管制情况而言,相比于10.07 IFR,SME IFR对于中国境内的外资半导体晶圆厂甚至给予了相对宽松的许可证政策。

问题七:

AC/S IFR 和SME IFR下对于美国人在中国境内的相关活动有无进一步的要求和限制?

10.07 IFR在EAR第744.6节下增设了对于美国人相关行为的出口管制限制在半导体业界激起了巨大的反响。BIS随后通过问答等形式,对于美国人的受限行为多次做了相应的澄清。而在此次AC/S IFR和SME IFR中,BIS没有另设新的相关限制,而是将原先澄清事项予以成文化,明确表达了受限制美国人支持行为的边界。这具体包括:

(1)明确了对美国人受限于EAR第744.6节相关限制应以知晓(knowledge)为前提条件,并明确要求美国人在开展相关业务前,应开展必要的尽职调查,如确认相关业务是否涉及“先进制程集成电路与其他传统集成电路”的“开发”或“生产”;

(2)明确了后道工艺(Back-End,如封测)以及仅从事半导体设计工作不受EAR第744.6节的相关限制;

(3)在EAR第744.6节中增加 (d)(1) 段,以明确美国人开展的行政和日常办事员工作(如财务审批等)和基础性研究活动(如大学教学)不属于EAR第744.6节下的禁止行为。此外,还增加了美国政府执法和情报行动的排除条款,明确规定第 744.6(c)(2)(i)至(iii)节中的“美国人”标准不延伸至进行美国政府执法和情报行动的 “美国人”;

(4)在EAR第744.6(d)(4)节中增加了适用于本节第(c)(2)(i)至(iii)段的排除条款。相关对美国人的限制不包含美国人为总部位于美国或A:5或A:6国别组区域的实体(该等公司的主要权益不能为总部位于澳门或D:5国别组区域实体拥有)雇用或工作的情形;

(5)在EAR第744.6(d)(5)节中增加了适用于本节(c)(2)(iii)段的排除条款,即美国人的出口管制限制不适用于维修(包括安装)活动,除非此类活动涉及先进制程半导体生产设施;

(6)除上述排除条款外,在EAR第744.6(c)(3)(i)(A)节中明确涉及许可证限制要求的活动是美国人不能“授权运输、传输或转运”相关可能用于先进制程半导体和先进计算的物项,同样也不能为先进制程半导体制造生产设施提供维护、修理、大修或翻新等支持活动,即使该等设施不属于EAR下受控物项。

总体而言,基于BIS本次在相关新规下的澄清,对于美国人的相关活动限制边界更为明确,对于美国人在包括中国在内的D:5国别组区域内开展业务提供了较为清晰的指引,并且大幅度减轻了外资半导体公司的涉美雇员在华开展业务的顾虑。

问题八:

如果继续在中国等地境内开展先进制程半导体相关业务,会有哪些风险?

在本次的相关新规中虽然没有明示在华开展先进计算和先进制程半导体生产、开发活动实体的可能处罚,但是基于本次发布的实体清单理由以及BIS在SME IFR新规中的相关说明,基本可以预测如果未来在华或其他D:5国别组开展先进计算芯片研发、AI训练和先进制程半导体制造业务,美国针对性的出口管制政策将成为不可忽视的风险。

在本次新规拟定过程中,曾有传闻BIS将针对性地发布一个“中国先进制程半导体生产设施清单”,将据信在中国境内开展先进制程业务的晶圆厂列入相关清单,直接适用EAR第744.6节和EAR第744.23节的相关限制。在本次SME IFR的问答中,BIS通过明确回应的方式表示该清单并非空穴来风,但是相关清单并未伴随着本次新规颁布而发布。BIS在回应中表示,本次随新规新增的13家实体清单已经表明了BIS在此事项上的态度。而从BIS在此次实体清单中的列名理由来看,在中国境内从事先进计算芯片开发(未来也可能包括先进制程半导体的生产、开发活动)已经属于EAR第744.11节所称的危害美国国家安全和外交利益的行为,BIS可以直接以此为由将相关实体列入实体清单。与此同时,BIS就先前讨论中部分评议者提到的部分美国人士可能会选择放弃美籍继续在华开展先进制程半导体开发业务相关事宜中也暗示,如果相关美国人放弃美籍,BIS后续可能也会将相关人等列入实体清单。当然,根据在部分公开场合的说明,BIS关于半导体出口管制新规中的先进制程半导体的相关标准可能会动态变化,建议企业需要结合自身的技术路线图和开发计划,妥善评估相关业务中的潜在风险,并适时做出相应调整。

结语

如我们一直所强调的,美国在半导体领域的相关出口管制措施具有明确的目标指向性和非常清晰的政策发展路径,对于中国企业而言,需要时刻保持对于相关政策发展的跟踪,了解潜在的政策风险,并将其作为商业决策的重要考量因素。未来在云计算等方面美国预计会进一步加强出口管制相关措施,并且半导体领域的出口管制措施也势必会和投资审查等其他领域的监管政策进一步合流,对此业内企业需要未雨绸缪,早做准备。另外,美国在半导体领域相关出口管制的经验预计也会在后续进一步应用到其他关键行业,如生物医药、电池等,对此,建议其他领域的中国企业也应当从半导体领域的出口管制风险应对中汲取经验,防患于未然。我们也将持续跟进美国相关贸易与政策动态,为大家带来相应解读。

————————

脚注:

[1] 总处理性能是 2x“MacTOPS” x“操作的位长”,是集成电路上所有处理单元的总和。

就 3A090 而言,“MacTOPS”是指乘法累加计算(D=AxB+C)每秒的理论峰值运算次数Tera(1012)。

TPP 公式中的 “2”是基于行业惯例,即在数据表中将一次乘法累加计算(D=AxB+C)算作 2 次运算。因此,2 x MacTOPS 可能与数据表中报告的 TOPS 或 FLOPS 相对应。

就 3A090 而言,乘法累加计算的“操作位长”是乘法操作输入的最大位长。

将集成电路上每个处理单元的 TPP 相加,得出总数。TPP = TPP1 + TPP2 + TPP3+··· + TPPn(其中 n 是处理单元的数量或集成电路上的处理单元)。

MacTOPS 速率按理论上可能达到的最大值计算。MacTOPS 速率推定为制造商在集成电路年度或手册中宣称的最高值。例如,4800 的 TPP 阈值可通过以下方式达到:600 tera 整数运算(或 2 x 300 'MacTOPS' )8 位或 300 tera FLOPS(或 2 x 150 'MacTOPS')16 位。如果集成电路设计用于多比特长度的 MAC 计算,可实现不同的 TPP 值,则应根据 3A090 中的参数评估最高 TPP 值。

对于 3A090 规定的可同时处理稀疏矩阵和密集矩阵的集成电路,TPP 值是处理密集矩阵(如无稀疏性)的值。

[2] 性能密度是 TPP 除以可适用芯片面积。就 3A090 而言,可适用芯片面积以平方毫米为单位,包括使用非平面晶体管架构的工艺节点制造的逻辑芯片的所有芯片面积。

[3] 19. The exporter has “knowledge” that it is or seeks to be producing at a facility where “production” of “advanced node ICs” occur, for a company headquartered in either Macau or a destination specified in Country Group D:5, an integrated circuit, or a computer, “electronic assembly,” or “component” that will incorporate (A) more than 50 billion transistors and (B) high-bandwidth memory (HBM).